1. 原语介绍

- 原语是 Xilinx 器件底层硬件中的功能模块,它使用专用的资源来实现一系列的功能。相比于 IP 核,原语的调用方法更简单,但是一般只用于实现一些简单的功能。本章主要用到了 BUFG、 BUFIO、 IDDR、 ODDR、IDELAYE2 和 IDELAYCTRL。

- IOB是Input/Output Block的意思 负责将外部引脚上的信号引入 FPGA 内部或者将 FPGA 内部的信号输出到外部引脚

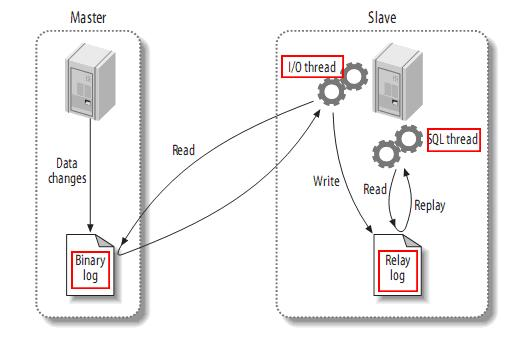

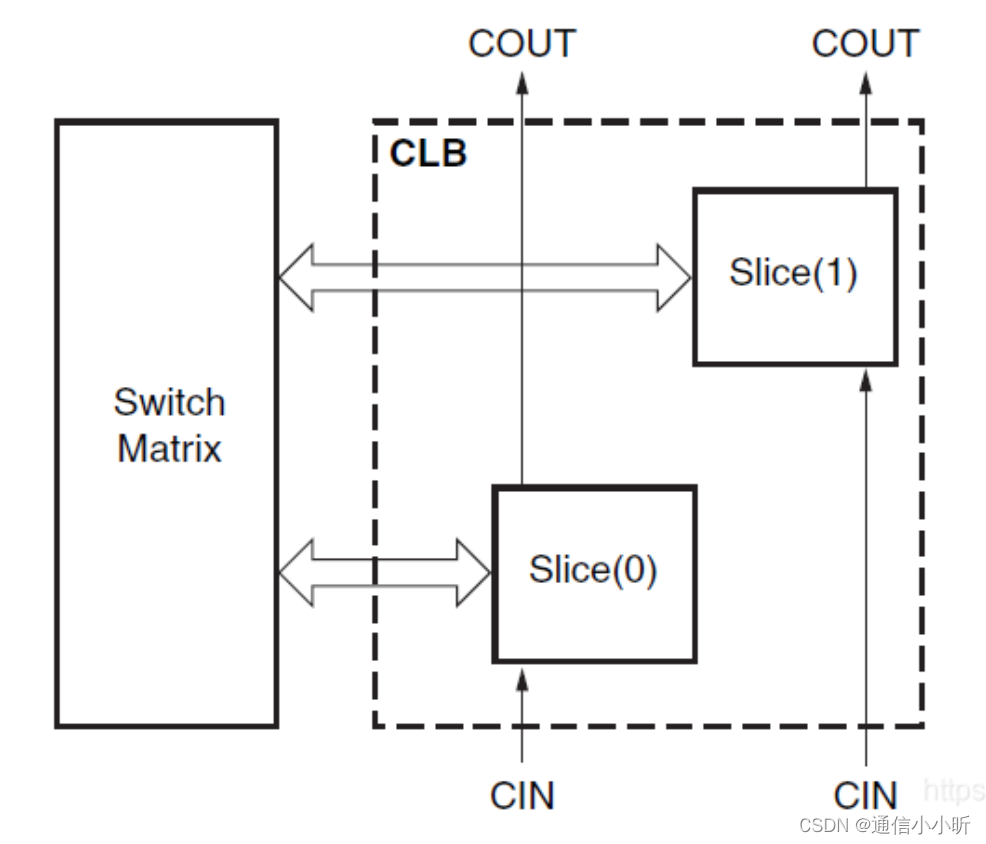

- CLB(Configurable Logic Blocks)的结构

- CLB是用于实现时序电路和组合电路的主要逻辑资源,CLB里有两个Slice,一个Slice等于4个6输入LUT+8个触发器(flip-flop)+算数运算逻辑

5. LUT本质上就是一个RAM。它把数据事先写入RAM后, 每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

5. LUT本质上就是一个RAM。它把数据事先写入RAM后, 每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

- CLB是用于实现时序电路和组合电路的主要逻辑资源,CLB里有两个Slice,一个Slice等于4个6输入LUT+8个触发器(flip-flop)+算数运算逻辑

2. BUFG

全局缓冲, BUFG 的输出到达 FPGA 内部的 IOB、 CLB、块 RAM 的时钟延迟和抖动最小,BUFG原语模板如下:

BUFG BUFG_inst (

.O(O), // 1-bit output: Clock output

.I(I) // 1-bit input: Clock input

);

除了 BUFG 外,常用的还有 BUFR, BUFR 是 regional 时钟网络,它的驱动范围只能局限在一个 clock region 的逻辑。 BUFR 相比 BUFG 的最大优势是偏斜和功耗都比较小。

3. BUFIO

BUFIO 是 IO 时钟网络,其独立于全局时钟资源,适合采集源同步数据。它只能驱动 IO Block里面的逻辑,不能驱动 CLB 里面的 LUT, REG 等逻辑。 BUFIO 原语模板如下:

BUFIO BUFIO_inst (

.O(O), // 1-bit output: Clock output (connect to I/O clock loads).

.I(I) // 1-bit input: Clock input (connect to an IBUF or BUFMR).

);

BUFIO 在采集源同步 IO 数据时,提供非常小的延时。但是不能驱动FPGA的内部逻辑,需要BUFIO和BUFG搭配起来使用以实现最佳的性能。如 ETH_RXC的时钟经过 BUFIO,用来采集端口数据; ETH_RXC 经过 BUFG,用来作为除端口采集外的其他模块的操作时钟。

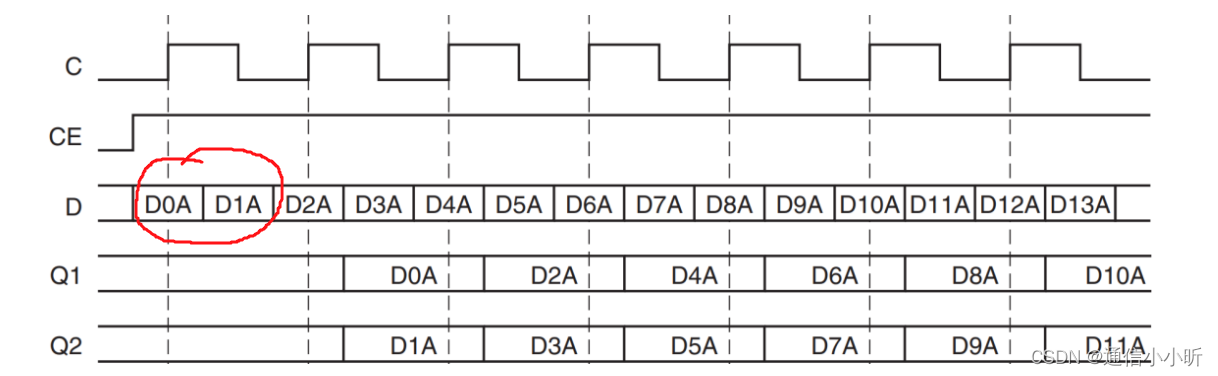

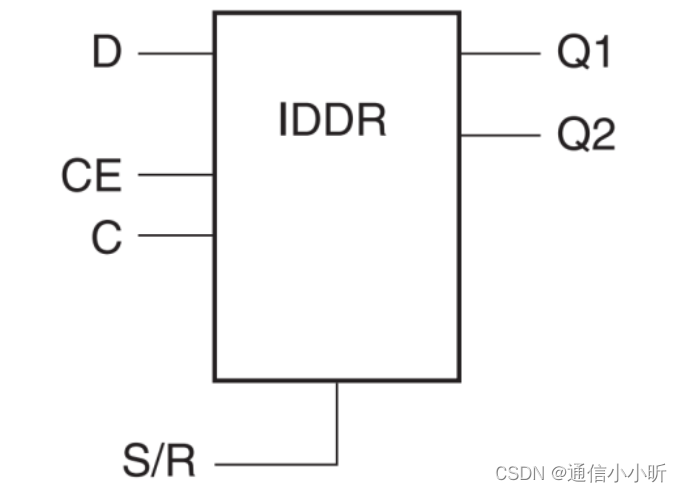

4. IDDR

在 7 系列设备的 ILOGIC block 中有专属的 registers 来实现 input double-data-rate(IDDR) registers,将输入的上下边沿 DDR 信号,转换成两位单边沿 SDR 信号。 IDDR 的原语结构图如下图所示:

C为输入的同步时钟 D为输入的1位DDR数据 CE是时钟使能信号 Q1和Q2分别是C时钟上升沿和下降沿同步输出的SDR数据

S/R置位/复位信号

IDDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

)IDDR_inst (

.Q1(Q1), // 1-bit output for positive edge of clock

.Q2(Q2), // 1-bit output for negative edge of clock

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D(D), // 1-bit DDR data input

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

一般使用SAME_EDGE_PIPELINED 模式。在时钟的上升沿输出 Q1 和 Q2, Q1 和 Q2 虽然在同一个 cycle 输

出,但整体延时了一个时钟周期。

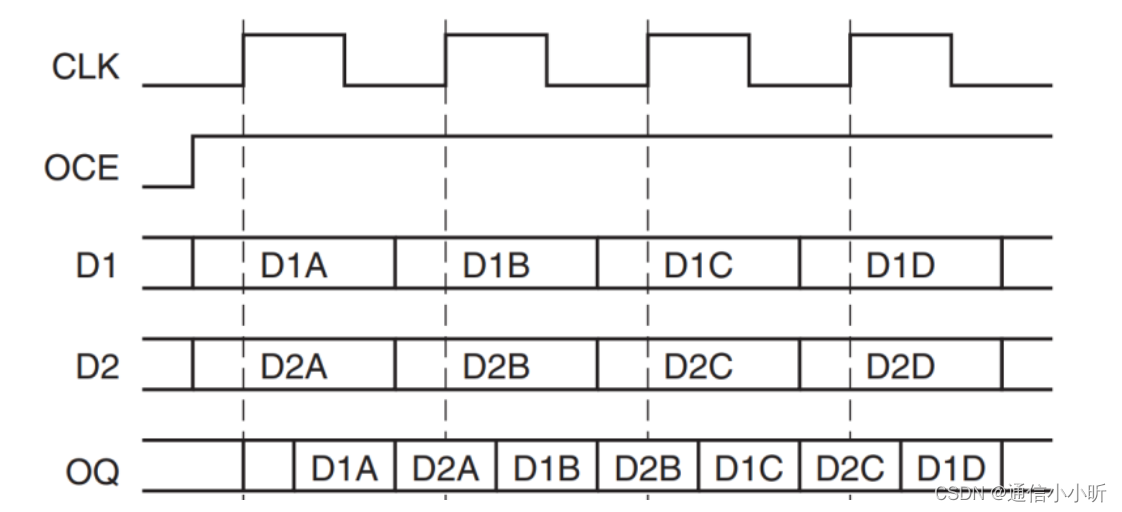

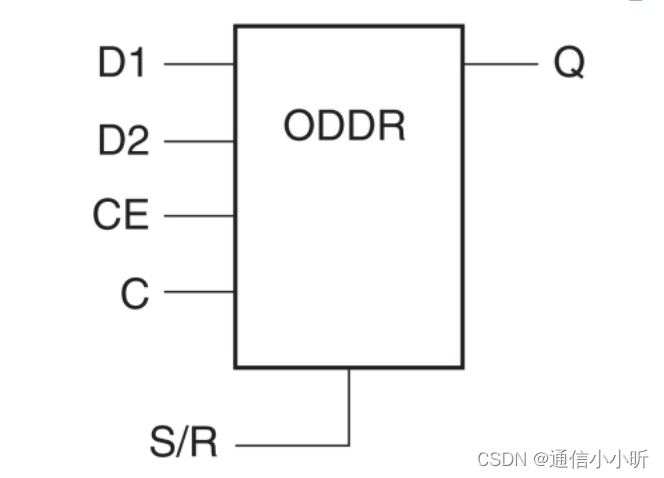

5. ODDR

通过 ODDR 把两路单端的数据合并到一路上输出

使用RGMII的时候,在发送者和接收者之间的数据的传输使用的都是DDR,但是在FPGA与PHY芯片通信之间使用的是SDR

ODDR原语示意图

ODDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_inst (

.Q(Q), // 1-bit DDR output

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D1(D1), // 1-bit data input (positive edge)

.D2(D2), // 1-bit data input (negative edge)

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

SAME_EDGE 模式使用的比较多,时序图如下图所示

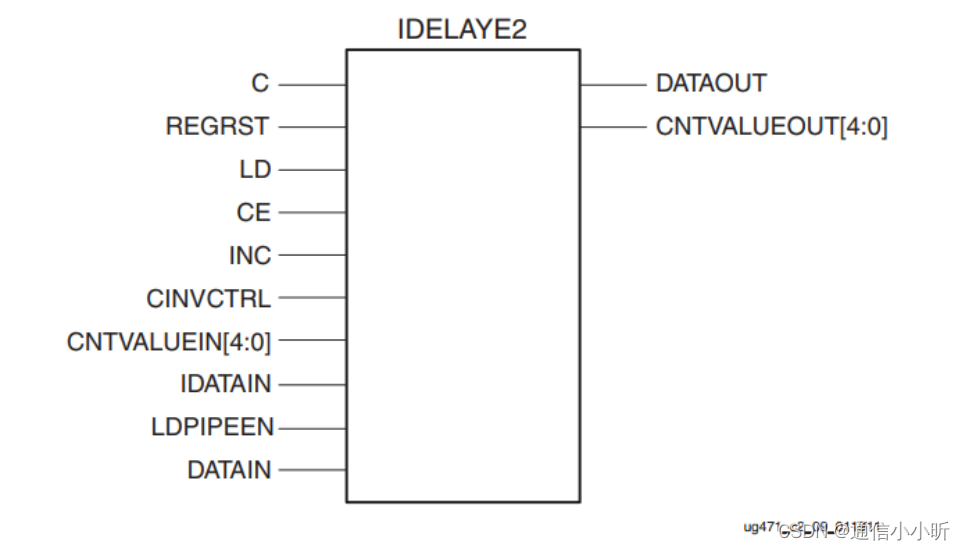

6. IDELAYE2

IO 延时原语,用于在信号通过引脚进入芯片内部之前,进行延时调节,一般高速端口信号由于走线延时等原因,需要通过 IDELAYE2 原语对数据做微调。

IDELAYE2 #(

.CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN)

.HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE")

.IDELAY_TYPE("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.IDELAY_VALUE(0), // Input delay tap setting (0-31)

.PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz

.SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal

)

IDELAYE2_inst (

.CNTVALUEOUT(CNTVALUEOUT),// 5-bit output: Counter value output

.DATAOUT(DATAOUT), // 1-bit output: Delayed data output

.C(C), // 1-bit input: Clock input

.CE(CE), // 1-bit input: Active high enable increment/decrement input

.CINVCTRL(CINVCTRL), // 1-bit input: Dynamic clock inversion input

.CNTVALUEIN(CNTVALUEIN), // 5-bit input: Counter value input

.DATAIN(DATAIN), // 1-bit input: Internal delay data input

.IDATAIN(IDATAIN), // 1-bit input: Data input from the I/O

.INC(INC), // 1-bit input: Increment / Decrement tap delay input

.LD(LD), // 1-bit input: Load IDELAY_VALUE input

.LDPIPEEN(LDPIPEEN), // 1-bit input: Enable PIPELINE register to load data input

.REGRST(REGRST) // 1-bit input: Active-high reset tap-delay input

);

和IDELAYE2 对应的还有 ODELAYE2,由于 A7 系列没有 ODELAYE2 原语,故此处不做讨论。

7. IDELAYCTRL

IDELAYCTRL 和 IDELAYE2 一般同时使用, IDELAYCTRL 对 IDELAYE2 延时进行校

准。 IDELAYCTRL 原语如下:

(* IODELAY_GROUP = <iodelay_group_name> *)

IDELAYCTRL IDELAYCTRL_inst (

.RDY(RDY), // 1-bit output: Ready output

.REFCLK(REFCLK), // 1-bit input: Reference clock input

.RST(RST) // 1-bit input: Active high reset input

);

8. 其他的原语

IODELAY_GROUP 为延时 IO 分组,一般数据接口位于多个 BANK 时,才需要分组。

IDELAYCTRL 通过参考时钟 REFCLK 来校准 IDELAY2 每个 tap 的延时值,可用的 REFCLK 频率为

190Mhz~210Mhz 或者 290Mhz~310Mhz。时钟频率越高对应的 tap 延时平均值越小,即延时调节精度越高。当参考时钟为 200Mhz 时,一个 tap 为 78ps。